The University of Manchester

# **AsipIDE** Tutorial

Bringing together GALS design and open-source tools in a hardware-software-FPGA co-simulation flow

Lilian Janin, Doug Edwards ASYNC-NOCS 2010

1

#### MANCHESTER 1824

The University of Mancheste

# **EU Project GALAXY**

GALs interfAce for compleX digital sYstem integration

Supported by

European Commission

7<sup>th</sup> Framework Programme (2007-2013)

Objective ICT-2007.3.3:

Embedded System Design

# **EU Project GALAXY**

#### GALAXY Project Partners

- IHP GmbH Innovations for High Performance Microelectronics (Germany)

- EPFL Ecole Polytechnique Fédérale de Lausanne (Switzerland)

- Università di Bologna (Italy)

- Silistix UK Ltd. (United Kingdom)

- Infineon Technologies AG (Germany)

3

#### MANCHESTER 1824

The Universit of Mancheste

# **EU Project GALAXY**

### GALAXY Project Goals

- Remove existing barriers to the adoption of GALS technology

- Integrated GALS design flow

- Interoperability framework between existing open and commercial CAD tools

- Heterogeneous systems at mixed levels of abstraction

- Novel Network-on-Chip capabilities

# **EU Project GALAXY**

- GALAXY Demonstrator:

Wireless communication system in 40nm CMOS process

- Evaluate GALS approach to solve system integration issues

- Prove robustness to process variability problems in nanoscale geometries

- Explore the low EMI properties, inherent low-power features

5

#### MANCHESTER 1824

The University of Mancheste

# **Tutorial Overview**

- General presentation of tools and IDE

- Demo of main features

- Hands-on: A home surveillance system

## General presentation of tools and IDE

- Motivation

- · Bringing GALS to the masses!

- Gcc brought software programming to home users

- Many open-source/freely-available hardware design tools

- Icarus Verilog simulator

- Xilinx ISE

- VHDL Alliance tools from Lip6

- But full open-source hardware-software-FPGA design flow still unclear

- Also integrates commercial tools

7

## MANCHESTER 1824

The University of Manchester

# General presentation of tools and IDE

- AsipIDE connects existing tools together to form a (co-)simulation design flow

- Iterative design methodology

- Transforming software...

- ...to hardware

- Hardware-software-FPGA co-simulation

- Automatically generated GALS communications

- Graphical debugging

- Multiple abstractions represented together

- Animation from simulation traces

# General presentation of tools and IDE

- Calculator demo

- Demonstrates iterative GALS prototyping

- Baseband processor&G3card demo

- Demonstrates scalable environment

- Navigation in large embedded system

- Features demo

9

#### MANCHESTER 1824

The University of Mancheste

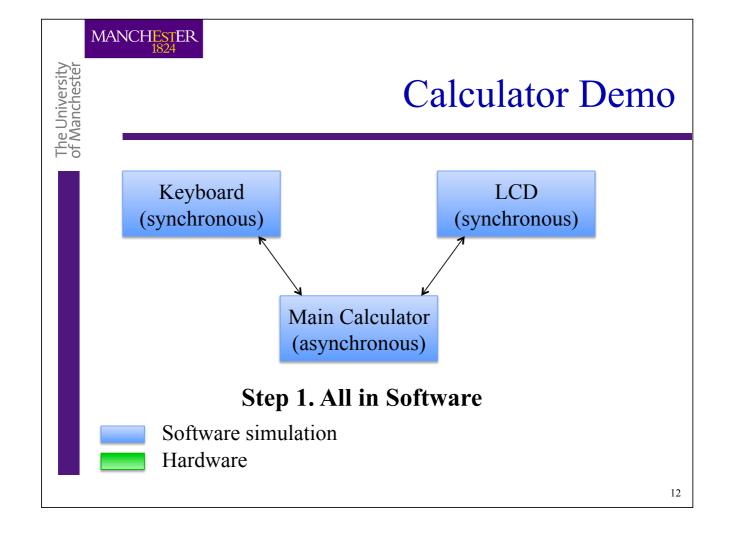

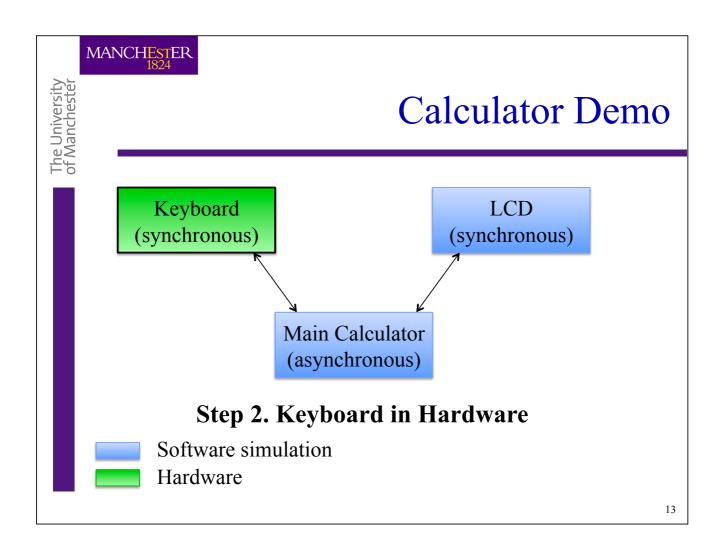

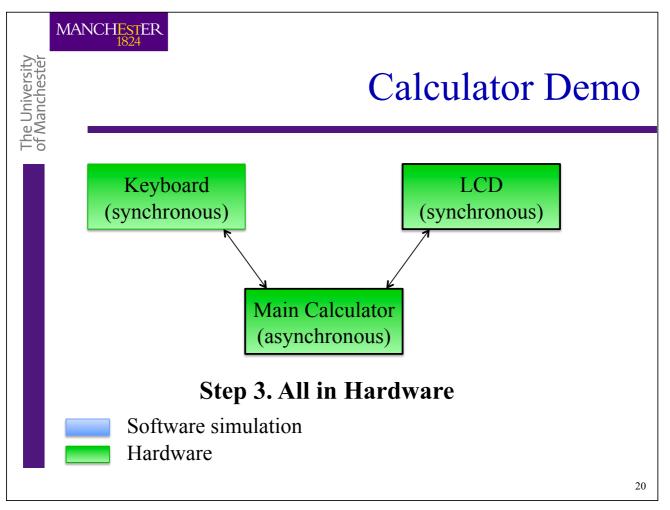

## Calculator Demo

- Calculator:

- Keyboard

- LCD

- Main program

- polling the keyboard

- processing

- sending value to LCD

- Keyboard asynchronous interface

- LCD asynchronous interface

## Calculator Demo

- High level architecture in C/C++

- Step-by-step implementation on hardware

- FPGA board prototyping

11

The University of Manchestel

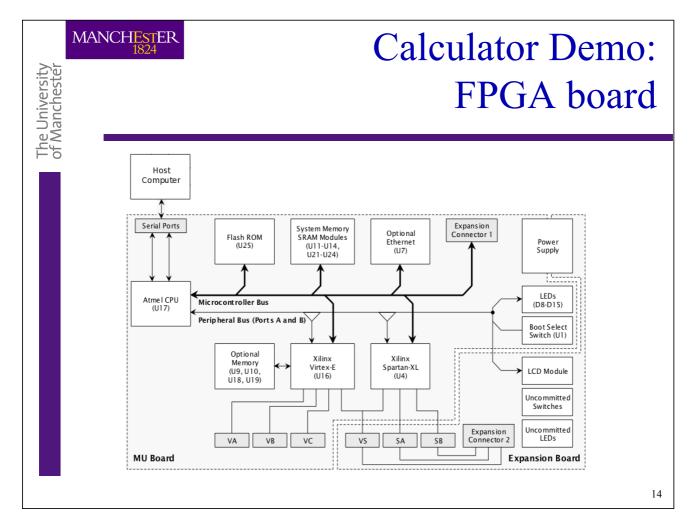

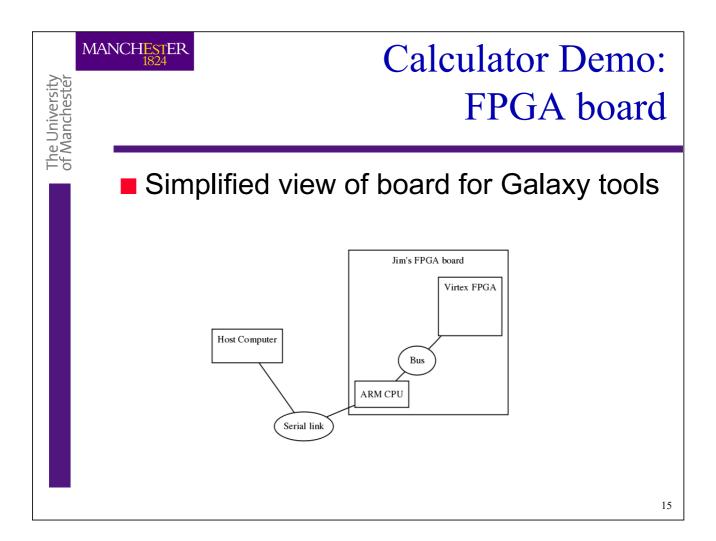

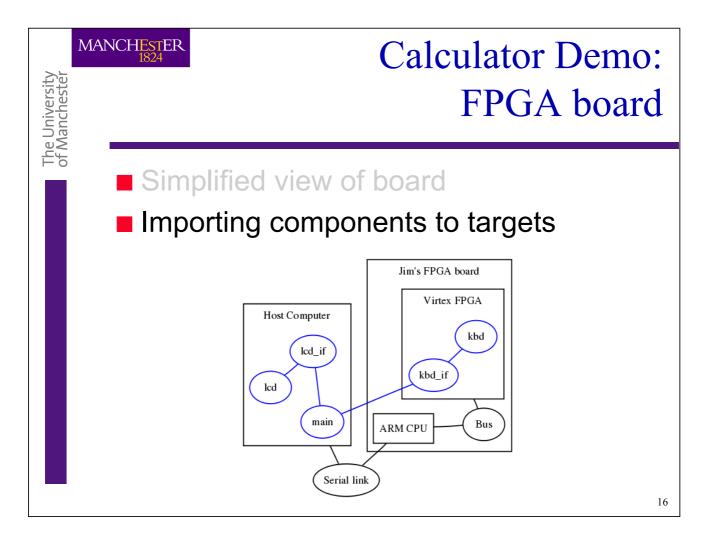

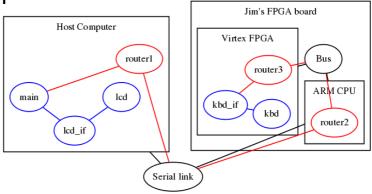

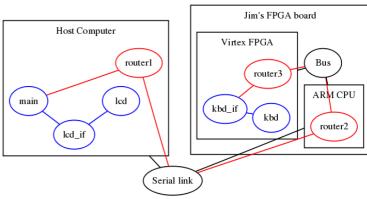

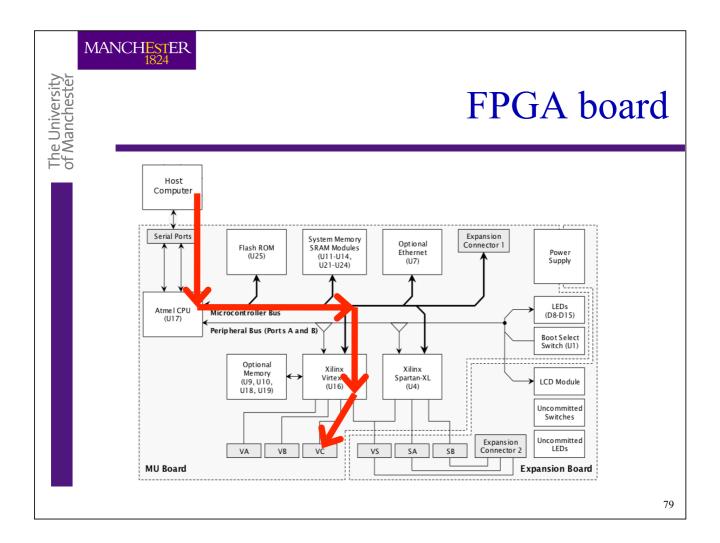

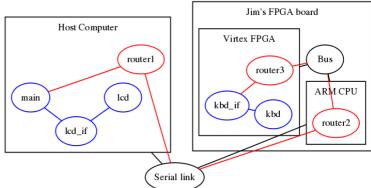

# Calculator Demo: FPGA board

- Simplified view of board

- Importing components to targets

- Links Analysis

• Impossible links re-routed

17

#### MANCHESTER 1824

# Calculator Demo:

# Hw-Sw Sync-Async Cosimulation

The Univers of Manchest

- Main execution on host

- SystemC transaction "poll keyboard"

- Sent to router1

- Routed through router2 and router3

- Converted to hardware asynchronous channel transaction

- Verilog keyboard\_if:

- Synchronous implementation

- Asynchronous interface

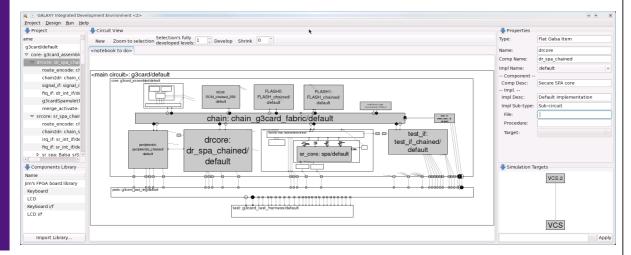

# Baseband processor&G3card Demo

- Illustrating scalability

- Zoom&pan inside large designs

Baseband processor&G3card Demo

The Record of the Process of the P

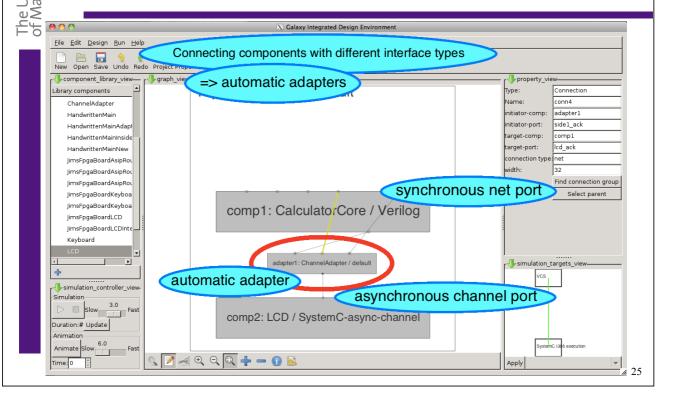

#### Features Demo

- Automatic instantiation of adapters

- Automatic use of transactors

- Easy to switch components between multiple levels of abstractions, with always a proper interface regenerated

- Selection of any simulators or FPGA target

- Ability to use asynchronous-specific simulators: Balsa, Petri nets

- Automatic use of local and remote tools for compilation, synthesis and simulation flow; remote resource sharing (queues)

- Trace file animation, debugging

- · Colour-based channel representation, clearer and saving space

- · Asynchronous debugging such as deadlock detection

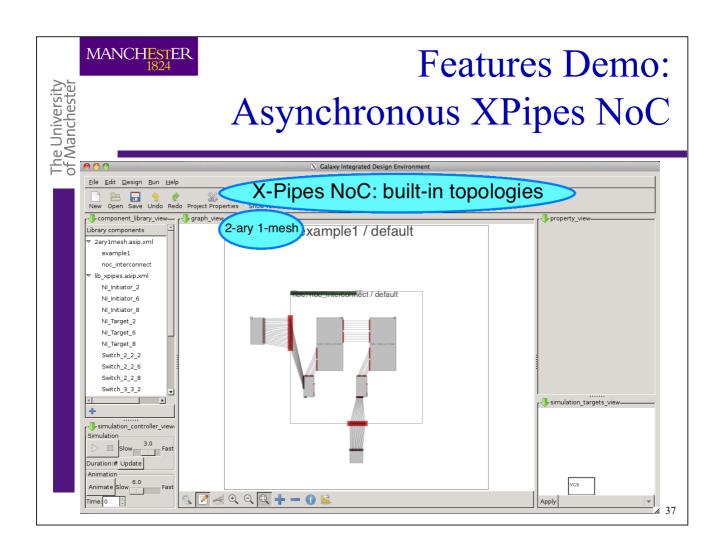

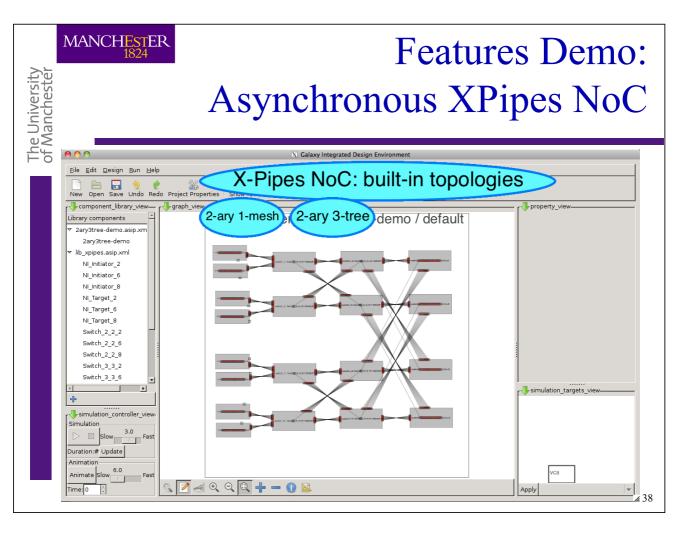

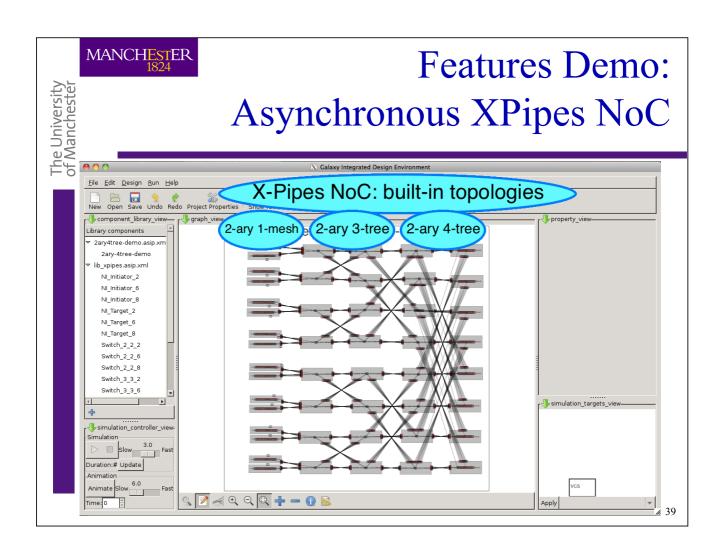

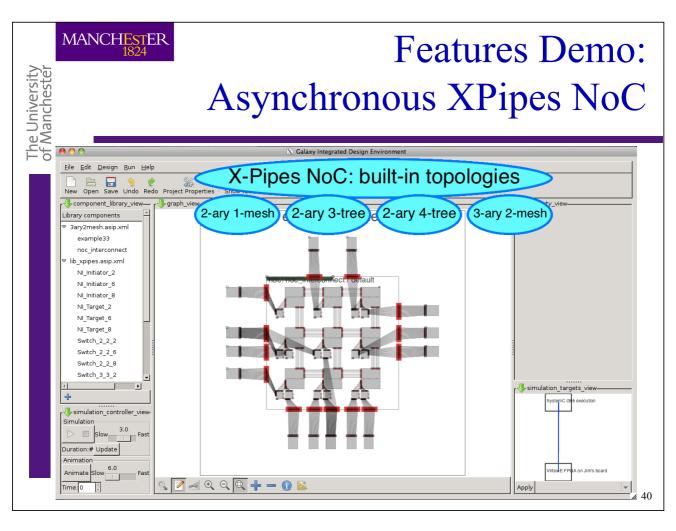

- Asynchronous NoC

- XPipes: graphical updates → regenerates everything automatically

23

#### MANCHESTER 1824

The University of Manchester

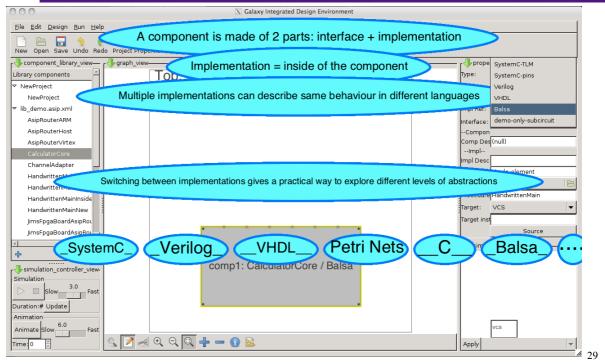

## Features Demo

#### Automatic instantiation of adapters

- Automatic use of transactors

- Easy to switch components between multiple levels of abstractions, with always a proper interface regenerated

- Selection of any simulators or FPGA target

- Ability to use asynchronous-specific simulators: Balsa, Petri nets

- Automatic use of local and remote tools for compilation, synthesis and simulation flow; remote resource sharing (queues)

- Trace file animation, debugging

- · Colour-based channel representation, clearer and saving space

- Asynchronous debugging such as deadlock detection

- Asynchronous NoC

- XPipes: graphical updates → regenerates everything automatically

### **Features Demo:**

# Automatic instantiation of adapters

### MANCHESTER 1824

The University of Manchester

- Automatic instantiation of adapters

- Automatic use of transactors

- Easy to switch components between multiple levels of abstractions, with always a proper interface regenerated

- Selection of any simulators or FPGA target

- · Ability to use asynchronous-specific simulators: Balsa, Petri nets

- Automatic use of local and remote tools for compilation, synthesis and simulation flow; remote resource sharing (queues)

- Trace file animation, debugging

- Colour-based channel representation, clearer and saving space

- Asynchronous debugging such as deadlock detection

- Asynchronous NoC

- XPipes: graphical updates → regenerates everything automatically

The University of Manchester

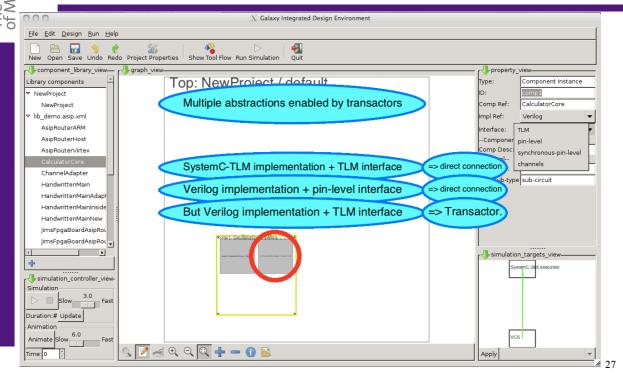

# Features Demo: Automatic use of transactors

## MANCHESTER 1824

The University of Manchester

- Automatic instantiation of adapters

- Automatic use of transactors

- Easy to switch components between multiple levels of abstractions, with always a proper interface regenerated

- Selection of any simulators or FPGA target

- Ability to use asynchronous-specific simulators: Balsa, Petri nets

- Automatic use of local and remote tools for compilation, synthesis and simulation flow; remote resource sharing (queues)

- Trace file animation, debugging

- Colour-based channel representation, clearer and saving space

- · Asynchronous debugging such as deadlock detection

- Asynchronous NoC

- XPipes: graphical updates → regenerates everything automatically

The University of Manchester

### Features Demo:

# Switching between abstractions

MANCHESTER 1824

The University of Manchester

- Automatic instantiation of adapters

- Automatic use of transactors

- Easy to switch components between multiple levels of abstractions, with always a proper interface regenerated

- Selection of any simulators or FPGA target

- Ability to use asynchronous-specific simulators: Balsa, Petri nets

- Automatic use of local and remote tools for compilation, synthesis and simulation flow; remote resource sharing (queues)

- Trace file animation, debugging

- · Colour-based channel representation, clearer and saving space

- Asynchronous debugging such as deadlock detection

- Asynchronous NoC

- XPipes: graphical updates → regenerates everything automatically

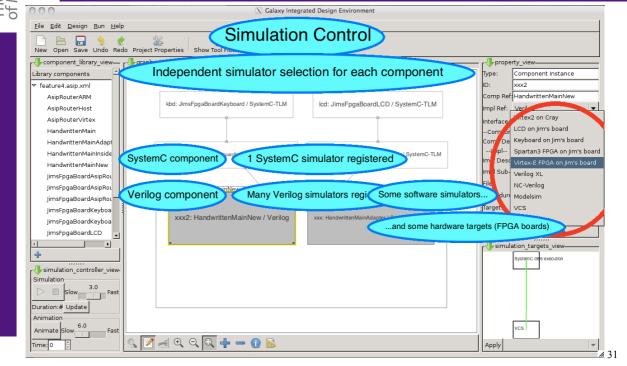

# Features Demo: Simulator/FPGA selection

### MANCHESTER

The University of Manchester

- Automatic instantiation of adapters

- Automatic use of transactors

- Easy to switch components between multiple levels of abstractions, with always a proper interface regenerated

- Selection of any simulators or FPGA target

- · Ability to use asynchronous-specific simulators: Balsa, Petri nets

- Automatic use of local and remote tools for compilation, synthesis and simulation flow; remote resource sharing (queues)

- Trace file animation, debugging

- Colour-based channel representation, clearer and saving space

- Asynchronous debugging such as deadlock detection

- Asynchronous NoC

- XPipes: graphical updates → regenerates everything automatically

The University of Manchester

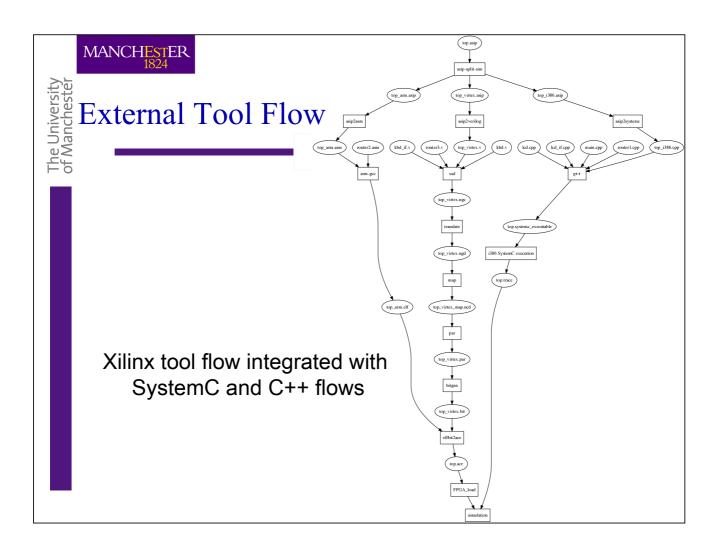

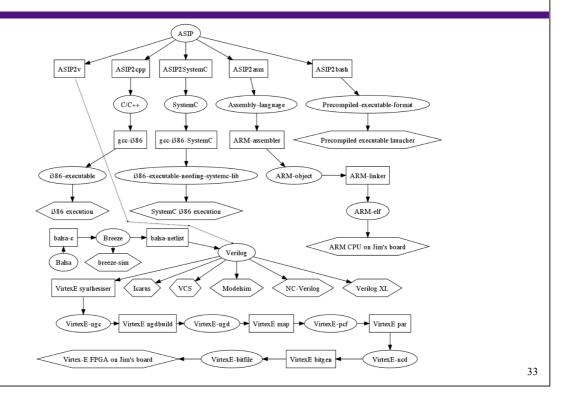

# Features Demo: Tool flows

#### MANCHESTER 1824

The University of Manchester

- Automatic instantiation of adapters

- Automatic use of transactors

- Easy to switch components between multiple levels of abstractions, with always a proper interface regenerated

- Selection of any simulators or FPGA target

- Ability to use asynchronous-specific simulators: Balsa, Petri nets

- Automatic use of local and remote tools for compilation, synthesis and simulation flow; remote resource sharing (queues)

- Trace file animation, debugging

- Colour-based channel representation, clearer and saving space

- Asynchronous debugging such as deadlock detection

- Asynchronous NoC

- XPipes: graphical updates → regenerates everything automatically

The University of Manchester

#### Features Demo:

# Trace file animation for debugging

#### MANCHESTER

The University of Manchester

## Features Demo

- Automatic instantiation of adapters

- Automatic use of transactors

- Easy to switch components between multiple levels of abstractions, with always a proper interface regenerated

- Selection of any simulators or FPGA target

- · Ability to use asynchronous-specific simulators: Balsa, Petri nets

- Automatic use of local and remote tools for compilation, synthesis and simulation flow; remote resource sharing (queues)

- Trace file animation, debugging

- Colour-based channel representation, clearer and saving space

- Asynchronous debugging such as deadlock detection

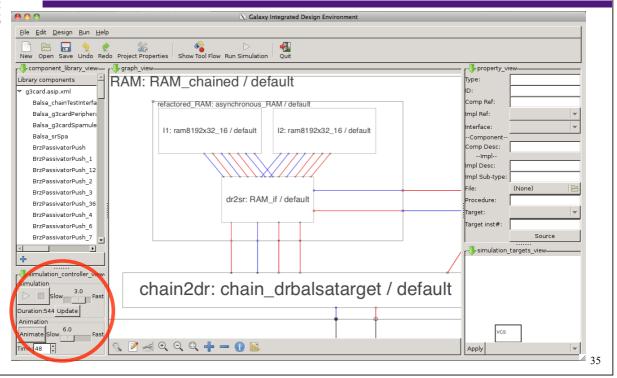

#### Asynchronous NoC

XPipes: graphical updates → regenerates everything automatically

#### Hands-on:

# A home surveillance system

#### Motivation

- Typical application which home developers would like to use FPGAs for, but encounter design flow problems

- Linux-based solutions available

- USB webcam

- Zoneminder analysis

- · Remote storage

- High purchase cost

- High consumption

- FPGA cheaper final solution

41

#### MANCHESTER 1824

#### Hands-on:

# A home surveillance system

# The Universi of Manchest

- Video processing application

- Webcam → motion detection → video encoding → ethernet streaming to remote server

#### Outline

- Requirements definition

- Identification of re-usable open-source components

- · Creation of components, architecture exploration

- · Components assembly, automatic adapters

- Automatic code generation, code running in SW

- Iterative refinement of SW components to HW

- Co-simulation software-FPGA

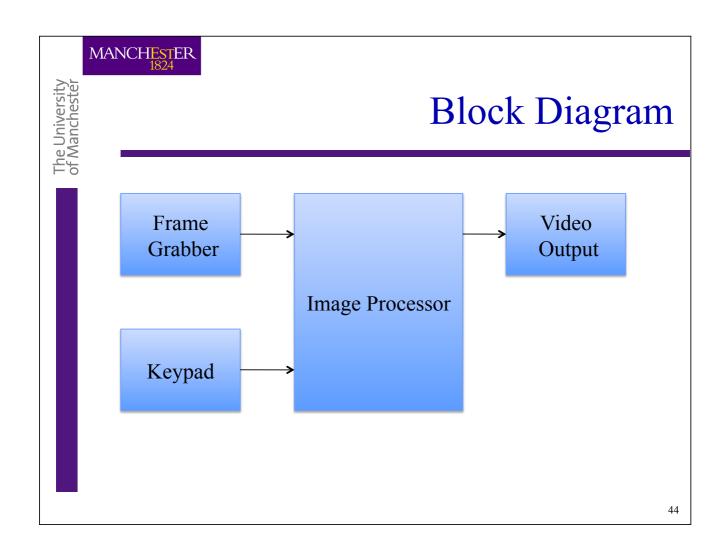

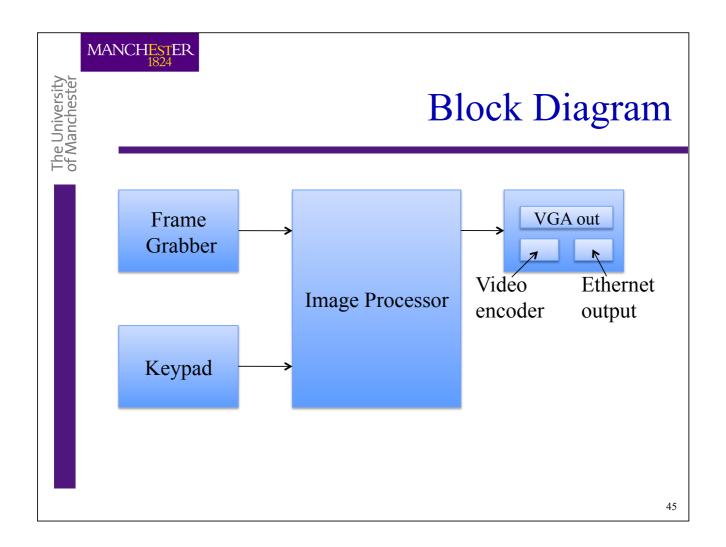

# Requirements Definition

- Inputs: webcam + keypad

- Outputs:

- Ethernet connection to send the motion-detected images/videos

- Replaced by local VGA output for the demo

- Movement is detected by subtracting 2 consecutive frames

- Changes in input frame pixels start the recording

- Threshold set by keypad

43

# Identification of re-usable open-source components

Available from www.opencores.org

- Keypad scanner

- JPEG-MJPEG video encoder

- VGA/LCD controller

- Wishbone Memory wrapper

### Start of Hands-on

- Initialise environment source asipide\_env\_setup

- Create and enter your own directory mkdir your\_name cd your\_name

- Start IDE asipide

51

Manchester

#### MANCHESTER 1824

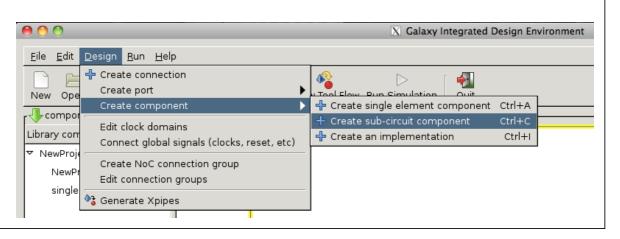

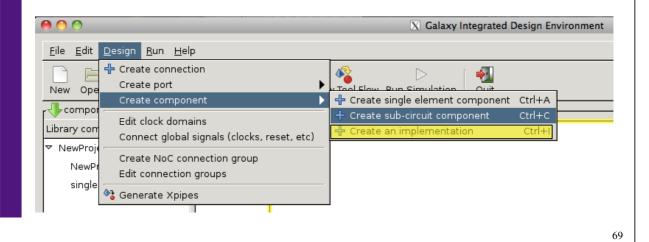

# Hands-on Step 1 - How to: Create a new component

- If it will contain sub-components

- · Select the parent component in the graphical design view

- Design Menu → Create component → Create sub-circuit component

- If it will be a "leaf" component, referring to existing source code files

- Select the parent component in the graphical design view

- Design Menu → Create component → Create single element component

# Step 1 - How to:

# Create a new component

- After a component creation, the IDE enters "Edit mode"

- · Components can be moved

- Components can be resized

- Next created component will inherit the same size

- You can edit the component and instance names in the Property View

53

#### MANCHESTER 1824

# Step 1:

# The Universit of Mancheste

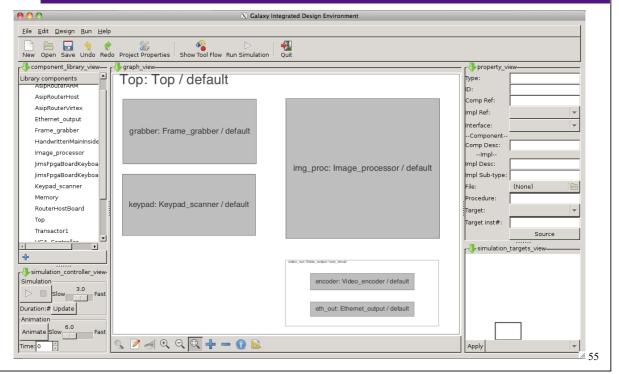

# Creation of component architecture

#### Create these 6 components:

- Image\_processor

- Frame\_grabber

- Keypad\_scanner

- Video\_output, with sub-components:

- Video encoder

- Ethernet output

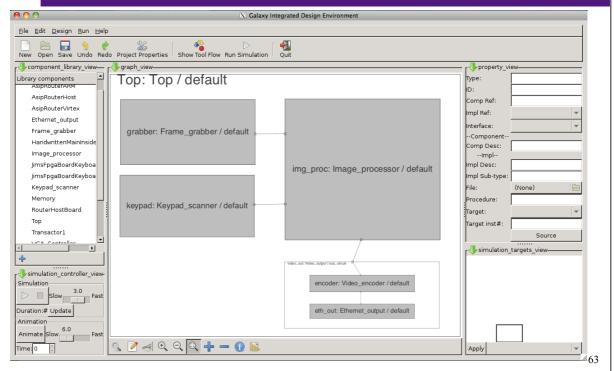

# Step 1 - Result: Created components

#### MANCHESTER 1824

The University of Manchestel

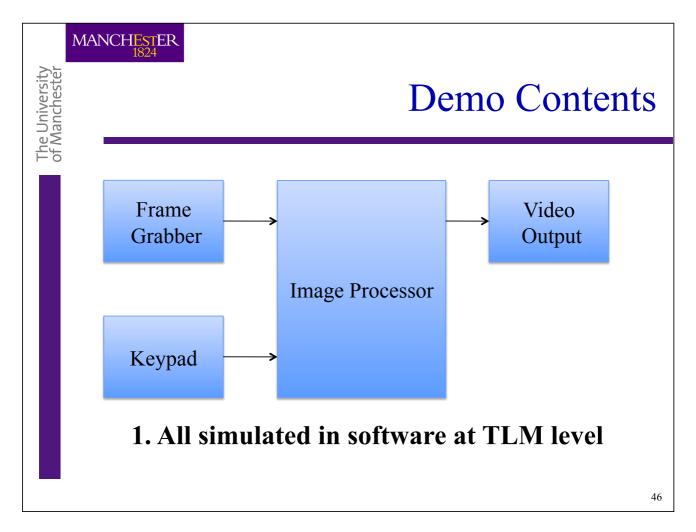

# Components assembly

- We will now import and assemble the components together

- Often the hardware is not available at the start of a project. We need to do as much as possible using software and simulators.

- → Version 1 (mostly to define the architecture and the main communication data types):

- Frame grabber component will take its input from files

- Ethernet output will dump results to a file

- Image processor will just subtract the new frame's pixels values from the previous frame's and check whether the max pixel change goes over a certain threshold

- Video encoder will use free software encoders: ffmpeg/libavcodec

- Communications will use TLM, the highest level of abstraction integrated in AsipIDE.

The University of Manchester

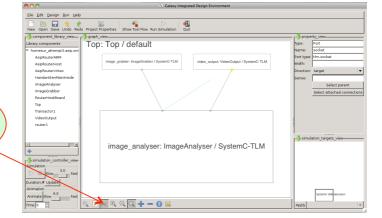

# Definition of ASIP communication types

- The *image processor* will be the main module (initiating requests)

- Initiates requests to frame grabber

- Sends probe requests to keypad scanner

- Provides commands and data to video output

- Create TLM ports for each component

- Select appropriately target or initiator

- Connect TLM ports

57

אומווכווכזנכו

MANCHESTER

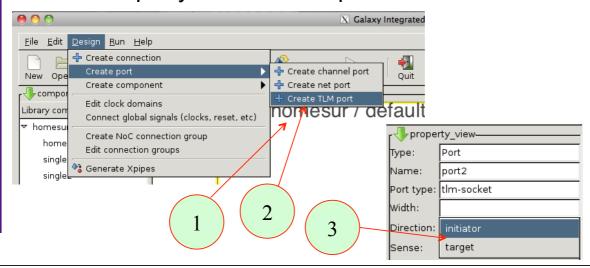

# Hands-on Step 2 - How to: Create a component port

- 1. Select component in the graphical design view

- 2. Design Menu → Create port → Create TLM port

- 3. In Property View: Select port direction

The University of Manchester

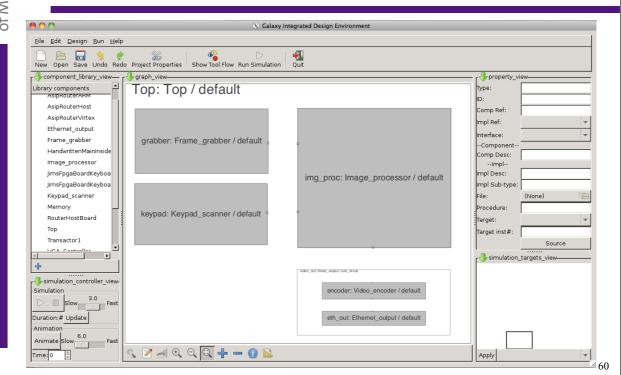

# Step 2:

# Creation of component ports

#### Create the following ports:

- Image processor

- 3 TLM initiator ports

- Frame grabber

- 1 TLM target port

- Keypad scanner

- 1 TLM target port

- Video encoder

- 1 TLM target port + 1 TLM initiator port

- Ethernet output

- 1 TLM target port

59

#### MANCHESTER 1824

ne University of Manchestei

# Step 2 - Result: Created ports

### MANCHESTER Hands-on Step 3 - How to: Connect two component ports

#### Several ways to do it, one being:

- Switch to "Connection mode" by clicking the first icon below the design view

- For each connection:

- Move the mouse near port 1

- · It should get highlighted when you are close enough

- Click and drag the mouse to port 2

- Release

- Deactivate "Connection mode" by clicking the first icon below the design view

Connection Mode Switch

# Step 3:

# Connecting components

## Create the following connections:

- Image processor → Frame grabber

- Image processor → Keypad scanner

- Video encoder → Ethernet output

- Image processor → Video encoder (Move the automatically created port to a better position)

62

The University of Manchester

# Step 3 - Result: Connected components

MANCHESTER 1824

The University of Manchester

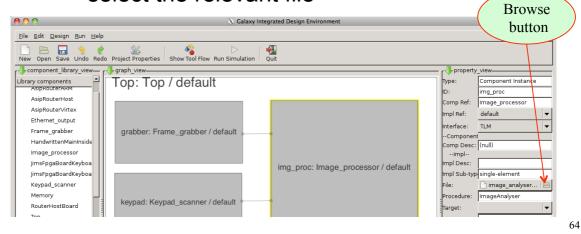

# Hands-on Step 4 - How to:

Assign source code to a component

- Select the component

- In Property View

• Use the File entry's "Browse..." button to select the relevant file

he University f Manchester

# Step 4:

# Component implementations

- We prepared a SystemC implementation for each component

- Available in directory ~/AsipIDE/SystemC/

- Assign the some source code to each component

- Image processor: image\_processor.cpp

- Frame grabber : frame\_grabber.cpp

- Keypad scanner: keypad\_scanner.cpp

- Video encoder: video\_encoder.cpp

- Ethernet output: ethernet\_output.cpp

65

### MANCHESTER 1824

1824

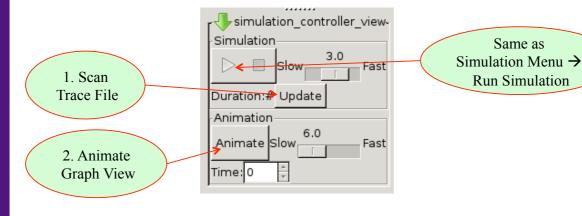

# Hands-on Step 5: SystemC simulation

- Start simulation

- Click Simulation Menu→Run Simulation

- Automatic generation of top-level SystemC code

- Reads input from directory images

- Streams output to file /tmp/asipide\_tutorial.mpg

- Output can be played with mplayer

he University f Manchester

# Debugging: Design view animation

- Simulation trace observable in IDE

- Controlled via Simulation controller view

67

#### MANCHESTER 1824

The University of Mancheste

# Connecting a real webcam

- Still in software

- New implementation of frame grabber

- Access to webcam from the host computer

- SystemC source code provided

# Hands-on Step 6 - How to: Create an extra implementation

- 1. Select component in the graphical design view

- Design Menu → Create component → Create an implementation

## MANCHESTER 1824

# Step 6:

# New component implementation

The University of Manchester

- Select the *frame grabber* component

- Create a new implementation

- Of type "single-element"

- Attached to the source code frame\_grabber\_webcam.cpp

- Check that the new implementaion is selected

- Simulate

The University of Mancheste

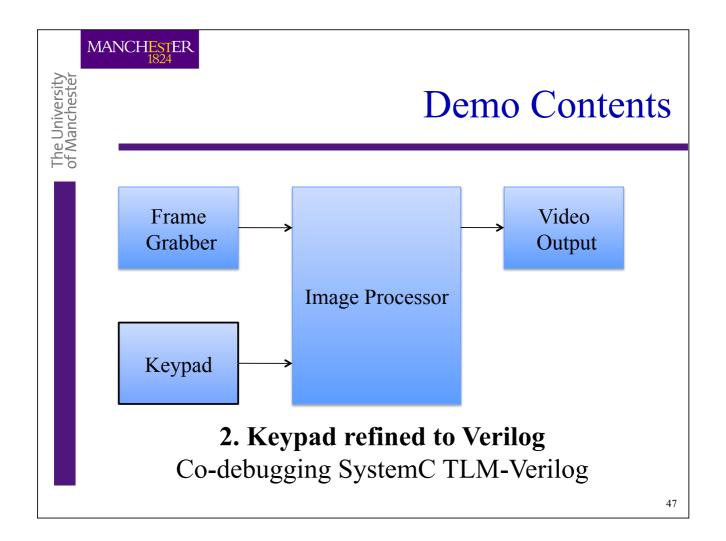

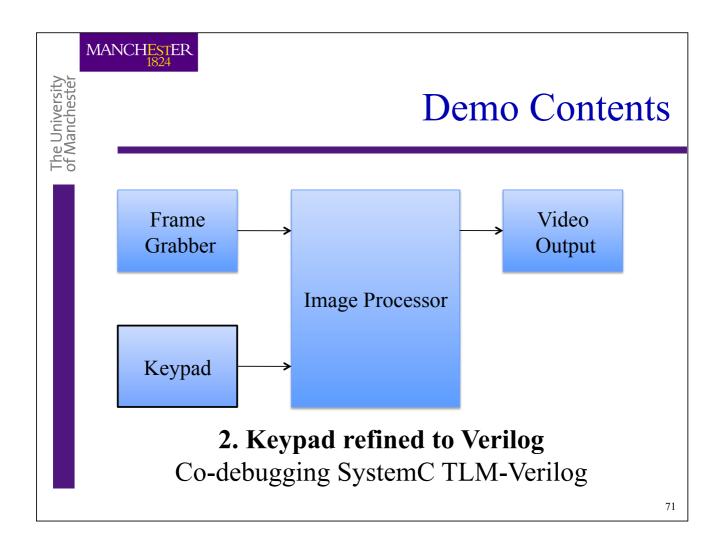

## Iterative refinement to hardware

- With everything working at TLM level, we will slowly move components to Verilog and then to hardware

- TLM ports refined to pin level

- Starting with the keypad

### Hands-on Step 7:

### Changing keypad to keypad v2

- Add library demo\_hardware\_lib\_1

- Drag&drop keypad v2 on top of keypad scanner

- 3. A new dialog suggests how the connections from the old component can be transferred to the new component. Accept the suggested mapping.

73

# Hands-on Step 7: keypad v2 inspection

- Select keypad v2 for inspection

- Two implementations

- Our first SystemC TLM implementation

- A new Verilog implementation

- Two interfaces

- TLM interface

- Pin-level interface

The University of Manchester

# Hands-on Step 7: *keypad v2* transactor

- Different combinations of implementation + interface possible

- TLM impl. + TLM interface

- as used until now

- · Verilog impl. + pins interface

- No connections between keypad\_v2's pins and image\_processor's TLM ports

- TLM impl. + pins interface

- We haven't defined a transactor for this, as we don't plan to simulate using this configuration

- Verilog impl. + TLM interface

- Useful to us, as the TLM interface can connect to the image\_processor's TLM ports

- Transactor automatically instantiated

75

MANCHESTER 1824

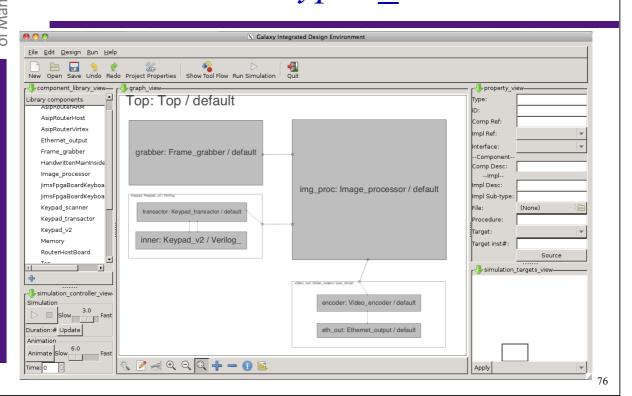

Step 7 - Result: *keypad v2* transactor

e University Manchester

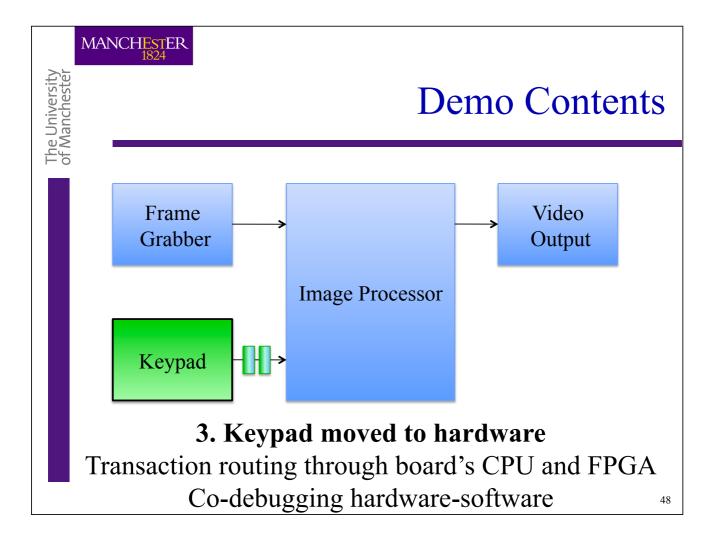

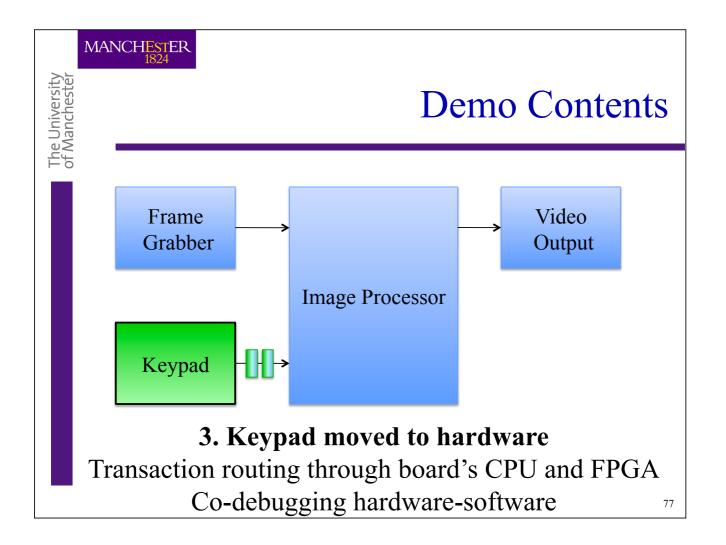

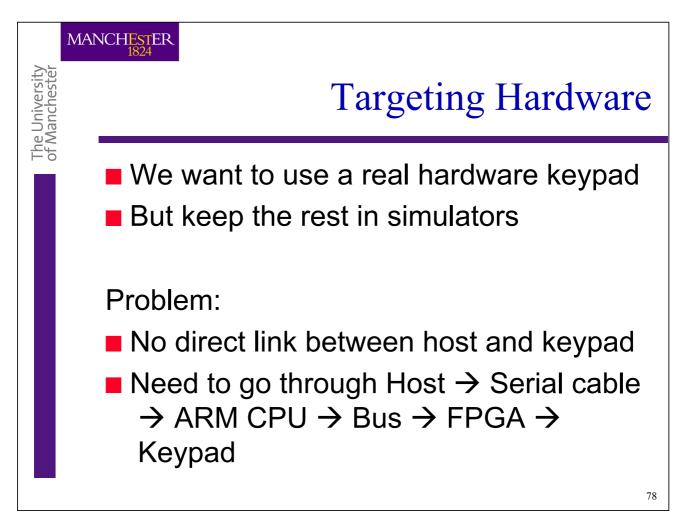

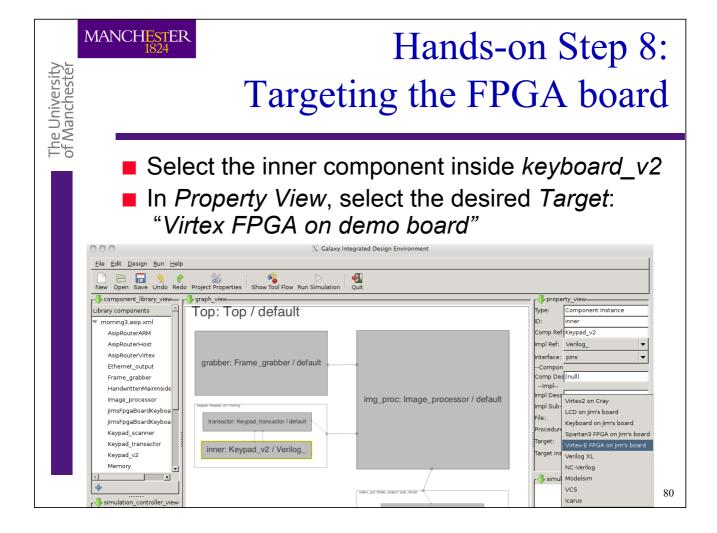

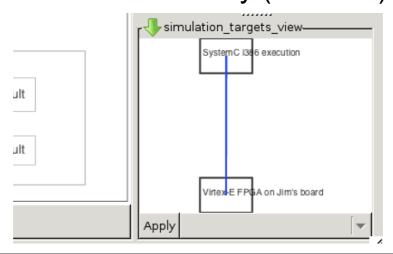

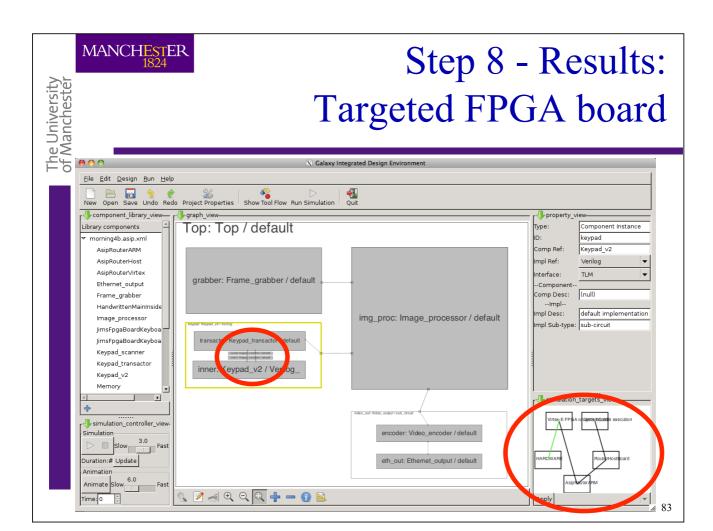

# Hands-on Step 8: Targeting the FPGA board

■ The Simulation targets view detects that the 2 simulation targets cannot communicate directly (blue link)

81

## MANCHESTER 1824

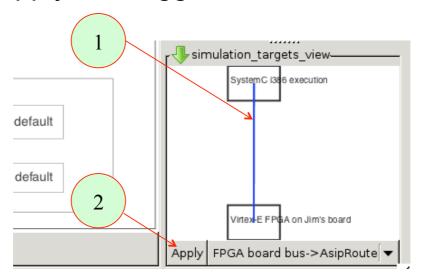

# Hands-on Step 8: Targeting the FPGA board

- 1. Select the blue link

- Apply the suggested ASIP routers

82

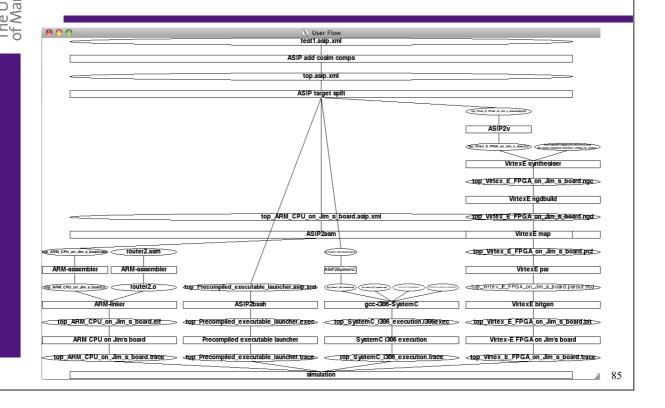

# Hands-on Step 9:

FPGA-software co-simulation

The University of Manchester

- Click on the icon "Show Tool Flow"

- Launching Simulation

- Generates SystemC to FPGA board communications

- Generates top-level code for each target

- SystemC

- Host to board controller (precompiled software)

- Board's ARM CPU

- Board's FPGA

# Step 9 - Results: Tool Flow

MANCHESTER 1824

Step 9 – Results:

Hardware-software co-simulation

- The Universit of Mancheste

- SystemC requests to the keypad module are forwarded to the hardware keypad via:

- Host to board controller

- Board's ARM CPU

- Board's FPGA

- Response forwarded back

The University of Mancheste

## Hw-Sw Sync-Async Cosimulation

- Main execution on host

- SystemC transaction "poll keyboard"

- Sent to router1

- Routed through router2 and router3

- Converted to hardware asynchronous channel transaction

- Verilog keyboard\_if:

- Synchronous implementation

- Asynchronous interface

The University of Manchester

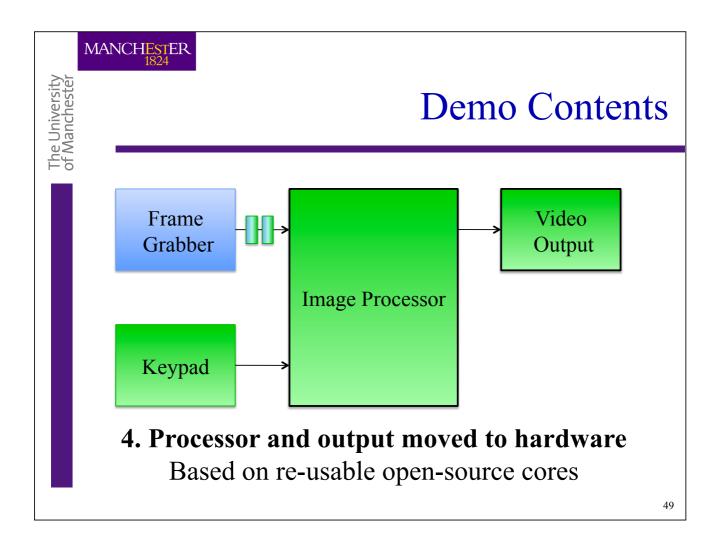

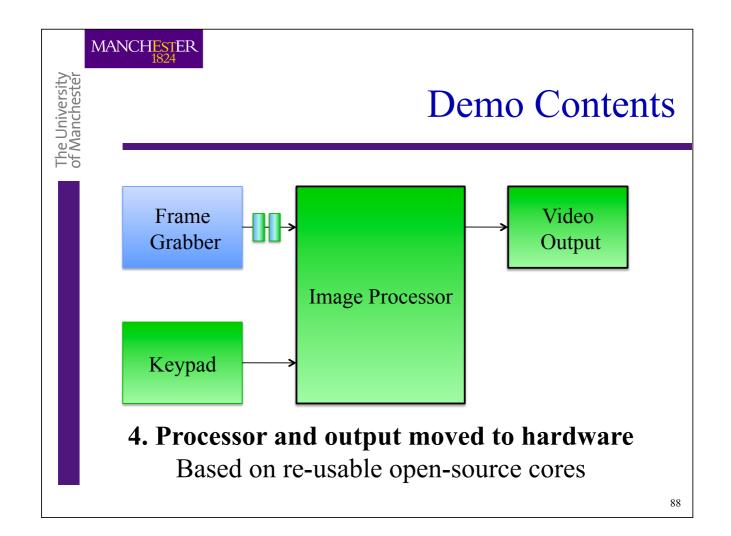

### Open-source IP Re-use

- IP re-use from www.opencores.org

- Video output

- VGA/LCD Controller

- Keypad scanner

- Keypad Scanner

- Frame grabber

- Hand-made component

- Opencores components use Wishbone interface

89

#### MANCHESTER 1824

The University of Mancheste

#### Final refinement to hardware

- Definition of ports at pin level

- Verilog implementations of modules

- All modules moved to FPGA

The University of Manchester

# Hands-on Step 10: IP Re-use

- Open and inspect tutorial\_final\_1.asip.xml

- This project illustrates how the cores from opencores.org were imported and connected together in a synchronous way (1 clock domain) with Wishbone interconnect

91

#### MANCHESTER 1824

## Hands-on Step 11:

### Integration in existing frameworks

The Universi of Manchest

- Launch Simulation

- Environment is setup to demonstrate interactive use of ISE within AsipIDE compilation/synthesis flow

- Instead of compiling and reporting errors in AsipIDE, designers can debug the Verilog inside ISE while other compilation branches (ARM ASM, SystemC, ...) follow their own tool flows

The University of Manchester

# Hands-on Step 12: Assisted GALS design

- Open and inspect tutorial\_final\_2.asip.xml

- This project illustrates "assisted GALS design"

- Same cores from opencores.org

- Wrapped by AsipIDE with GALS interfaces

- Can serve to bootstrap GALS project or to learn about GALS

93

#### MANCHESTER 1824

The University of Mancheste

## Quick Peek

- Feature coming soon: Embedded visualisation of HDL

- E.g. Verilog components will show their inner synthesised netlist

- Trace file events will be animated on the netlist in the GUI

- Multiple languages visualised simultaneously

he University f Manchester

# AsipIDE Tutorial

# Thank You!

9: